Intel files patent for Forksheet Transistor

| 01-02-2022 | By Robin Mitchell

Intel has recently filed for a new patent regarding the next generation of transistor design; the Forksheet transistor. What challenges does Moore’s Law present, what are Forksheet transistors, and what technology will succeed this?

What challenges does Moore’s Law present?

By far, the most significant factor that has helped advanced technology is the ability to reduce the size of transistors. The power of a computing device determines what it can do, and the more powerful a computer is, the more it can do. Since computing power is a function of how many operations can be performed per second and the size of data that can be operated on, increasing the number of transistors on a chip by reducing their size makes sense. Smaller transistors operate on lower voltages, allow for faster switching times, and allow for more transistors to fit.

Since developing the first integrated circuits, semiconductor companies faced multiple challenges such as crystal refinement, economic methods for producing masks, and designing new circuitry that can help accelerate computing operations. However, fast forward to modern integrated circuit design, and the challenges faced are different on a fundamental level.

One typical example is electron tunnelling, the quantum effect whereby electrons can effectively teleport through a dielectric material. Large transistors built in the 90s never saw this as a problem as such quantum effects are only observed in the nanometre scale. Transistors today, however, are rapidly approaching the angstrom size (less than 1nm), and at this scale, electron tunnelling becomes a major challenge. This tunnel essentially results in current leakage, and this leakage creates transistors with poor switching characteristics and increases energy consumption.

Another example is physical size. Reducing a transistor from 250nm to 50nm is difficult, but both are made from hundreds of thousands of atoms (if not millions). However, transistors on the nanometre scale are made of a few thousand atoms or less, which means that individual atoms start to affect the performance of a transistor. Eventually, transistor features will become so small that the wrong placement of individual atoms could prevent a transistor from operating.

These factors will see Moore’s Law, the idea that transistor count doubles every two years, start to fall apart. And when this happens, new innovations in the industry will no longer be able to rely on increasing transistor counts.

What are Forksheet transistors?

Recently, Intel filed for a patent describing the use of Forksheet transistors, and it is believed that these will drive the next generation of devices. But what exactly is a “Forksheet Transistor”, and how does it differ from Intel’s recent announcement on RibbonFETs?

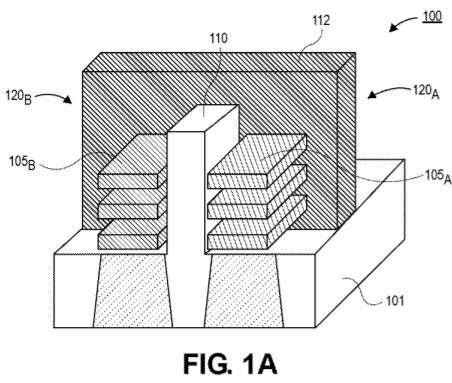

In essence, a Forksheet transistor utilises the same nanoribbon technology seen in RibbonFETs to produce active devices. While RibbonFETs are individual transistors (such as N and P type), the Forksheet transistor combines these two into a single device with a dividing dielectric between the N and P channels. Thus, a complementary device is produced in the same of a single transistor, which helps reduce energy consumption and space usage.

Image courtesy Intel

Combining the N and P-type transistor into a single package is especially advantageous for modern logic circuits as CMOS requires the use of complementary pairs. This transistor design doesn’t imply that the N and P-type transistors are connected, but it provides both transistors with the same gate.

What technology will succeed this?

It cannot be said for sure what technology will succeed Forksheet transistors, and there isn’t even a guarantee that Forksheet transistors will leave the laboratory. What can be said of future technology is that it will be physically smaller than devices currently made today, and the use of vertical designs will likely be popular. This is because most semiconductors are planar devices and make no use of the vertical space for active devices.

If researchers fail to shrink transistors further, then going up will be significantly easier than shrinking down. Furthermore, researchers may look towards systems on modules to combine multiple integrated circuits created separately and then wired together. This helps to improve chip yields during manufacture, and it also allows for increased performance compared to using multiple integrated circuits on a PCB separated by some distance.