Terahertz Wireless Links Enable Next-Gen Processors

Insights | 09-09-2025 | By Robin Mitchell

Key Things to Know:

- Interconnect bottlenecks in CPUs and QPUs are now as limiting as transistor performance, slowing overall system scaling.

- Terahertz (THz) wireless links, using phased-array transmitters and quantum-inspired receivers, aim to replace resistive copper wiring.

- Floquet-engineered semiconductor materials can enhance receiver sensitivity while reducing energy-intensive signal correction.

- Hybrid strategies combining THz and optical interconnects may provide scalable solutions for both classical and quantum processors.

As computing demands intensify, the pressure to scale processor performance has led to remarkable advances in transistor design. Yet, a subtler bottleneck has emerged, one that lies not within the transistors themselves, but in the wiring between them. Known as interconnects, these metallic pathways are struggling to keep pace with the speed and complexity of modern CPU and QPU architectures.

What makes interconnects such a critical limitation? How are researchers proposing to replace traditional wiring with terahertz wireless links? And could this approach transform the design of future chips?

The Challenge with Interconnects in CPUs and QPUs

As transistor counts continue to rise and feature sizes shrink, engineers face increasingly subtle and fundamental obstacles. Quantum effects in channels, the atomic granularity of materials, and signal integrity during rapid switching have all forced innovation in device design and fabrication. Yet even as transistors themselves advance, a more persistent problem has emerged: interconnects within the chip.

Modern CPUs and QPUs are no longer single-core processors; large multicore systems require data to move efficiently between disparate regions of the die. This seemingly simple task is complicated by signal delay, bandwidth limitations, and integrity issues. As the physical distance between cores grows, wire resistance and capacitance slow signals, while multiple metal layers introduce additional propagation delays and cross-talk.

Layer transitions and complex routing exacerbate the problem. Signals must traverse vertical vias, navigate through congested metal layers, and avoid interference, all while maintaining timing margins for high-frequency operation. These constraints make scaling to hundreds of cores on a single die increasingly difficult. In practice, interconnect design is now a limiting factor in overall chip performance, rivalling transistor speed and logic efficiency as the primary bottleneck in next-generation CPUs and quantum processors.

Terahertz Wireless Links: Breaking the Wiring Bottleneck

A radical alternative that some believe could be the key to these challenges is to replace wires with waves. Recently, researchers have proposed a chip-scale terahertz (THz) wireless architecture that leverages a modular phased-array transmitter and a nanoscale quantum-inspired receiver. The transmitter sculpts energy into tightly focused, near-field beams, while a dual-carrier configuration suppresses unwanted grating lobes and mitigates polarisation mismatches. This enables precise, high-bandwidth communication between cores or chips at near-light speed.

One notable advantage of the phased-array approach is its ability to direct power precisely where needed, minimising leakage into neighbouring circuits. This selective targeting not only improves spectral efficiency but also reduces the electromagnetic interference that typically hampers dense chip environments. Early studies suggest that terahertz phased arrays could outperform conventional millimetre-wave designs in both stability and scalability, making them a practical path towards wireless interconnects.

On the receiving side, a two-dimensional semiconductor quantum well (2DSQW) employs Floquet engineering to tailor electron responses to incoming THz radiation. By modulating the material’s effective conductivity in time, the receiver emphasises the desired signal while suppressing noise, all without heavy post-processing. Spatial modulation allows information to be encoded in current-flow patterns, making the link compact, sensitive, and robust against interference.

The use of Floquet-engineered 2D semiconductor quantum wells also offers a route towards tunable receivers, where device characteristics can be dynamically adjusted in response to changing workloads. This adaptability could help overcome one of the key challenges of chip-to-chip communication: maintaining consistent link quality under variable data traffic and thermal conditions. By embedding such dynamic features at the material level, researchers aim to reduce dependence on energy-intensive digital correction stages.

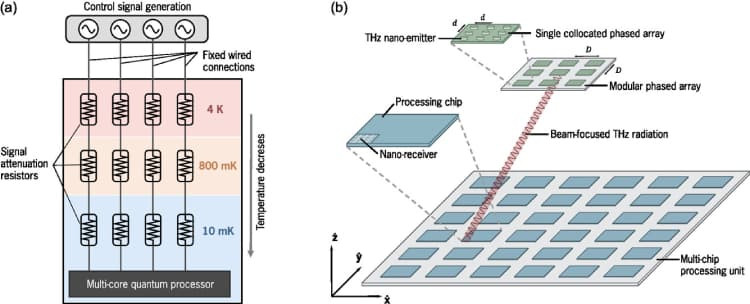

To better illustrate the shift from traditional wired connections to wireless terahertz links, Figure 1 contrasts two approaches.

Figure 1. (a) Schematic of a conventional coaxial wiring scheme for multichip quantum processors, with color-coded regions indicating the temperature gradient from signal sources to the quantum chips. (b) Wireless interconnect fabric using a modular phased array (MPA) that beam-focuses terahertz (THz) radiation onto nanoreceivers integrated within each processing unit of the multicore system.

For classical processors, the benefits are clear: long, resistive wires are removed from critical paths, reducing energy per bit and increasing bandwidth. In quantum systems, wireless links offer modest reductions in control-line density and thermal load, preserving cryogenic stability while alleviating one of many scaling challenges.

Another area of interest lies in the hybrid use of terahertz wireless and optical links. While optical interconnects excel at longer distances and higher aggregate bandwidth, terahertz channels could complement them in short-range, intra-package environments where compactness and low power are critical. Integrating both approaches may provide a layered communication strategy, balancing efficiency with flexibility across classical and quantum computing platforms.

Could Terahertz Waves Be the Answer?

It is becoming increasingly clear that traditional electronic interconnects cannot keep pace with the performance demands of modern processors. Resistance, capacitance, and cross-talk are now fundamental barriers to scaling, and something different is required.

Optical systems are one strong candidate, offering high bandwidth and immunity to electrical noise. Microwaves are another, already proven in wireless communications, but now being reconsidered for on-chip and chip-to-chip links. Terahertz waves, sitting between these two domains, represent a particularly compelling option. By bouncing high-frequency energy around a chip’s cavity, engineers could achieve efficient, high-integrity signal transmission that copper wires simply cannot provide.

Light and high-energy microwaves allow clear separation between frequency bands, enabling massive parallelism in communication channels. Noise introduced during transit is minimal, and in-silicon circuits could handle modulation, routing, and detection directly, keeping the entire system compact and integrated. In effect, the chip would stop relying on a tangle of wires and instead operate as a carefully orchestrated electromagnetic structure.

For now, however, copper and silicon traces still dominate interchip communication. They are mature, cheap, and well understood. However, the trajectory of performance demands is not slowing, and the wiring bottleneck is only tightening. The real question is not whether terahertz or optical systems will replace traditional interconnects, but when.