Capacitorless DRAM Unlocks 3D Integration and Efficiency

Insights | 02-05-2025 | By Robin Mitchell

As computing systems grow ever more powerful and interconnected, the memory technologies that underpin them are being pushed to their limits. Among these, Dynamic Random Access Memory (DRAM) has long been a cornerstone of modern electronics, enabling rapid data access across everything from smartphones to supercomputers. But with demand surging for higher speeds, greater densities, and lower power consumption, traditional DRAM designs are beginning to show their age.

Key Takeaways:

- Traditional DRAM technology is facing critical limitations in scalability, speed, and energy efficiency due to its capacitor-based architecture.

- Imec’s new 2T0C DRAM design uses IGZO-based transistors to eliminate the capacitor, offering longer data retention and lower power consumption.

- This capacitorless DRAM is compatible with back-end-of-line fabrication, enabling high-density 3D stacking and integration with logic circuits.

- Capacitorless IGZO DRAM is a promising candidate for next-generation memory solutions, including embedded DRAM and universal storage systems.

What are the fundamental limitations of DRAM technology, how are researchers responding, and what promise do innovations like capacitorless DRAM cells hold for the future of memory architecture?

The Evolution and Challenges of DRAM Technology

The introduction of Dynamic Random Access Memory (DRAM) has played a pivotal role in the computing revolution of the past 50 years. This technology has been instrumental in providing users with faster and more efficient access to information, enabling rapid advancements in fields such as artificial intelligence, machine learning, and data analysis. At its core, DRAM consists of a single transistor and capacitor design, allowing for the storage of binary data in the form of charged or discharged capacitors. This foundational architecture has been a cornerstone of the industry, but as technology continues to advance, it faces a multitude of challenges that threaten its continued relevance.

Scaling Challenges in Modern DRAM Design

The need for higher density and faster access times has led to a relentless pursuit of miniaturization, resulting in DRAM cells that are increasingly smaller. While this reduction in size may seem beneficial, it also presents a range of challenges that can compromise the performance and reliability of memory storage.

One of the primary limitations of traditional DRAM is the presence of capacitors, which contribute to increased charge and discharge time. As memory access speeds continue to accelerate, the time taken for capacitors to charge and discharge becomes a significant bottleneck. This slowdown in memory speed not only hampers the overall performance of computing systems but also results in increased power consumption, making it a critical concern for energy-efficient designs.

Rising Memory Access Demands and the Search for Alternatives

Another significant challenge faced by DRAM technology is the reduction in capacitance as cell sizes decrease. While smaller cells are essential for achieving higher densities, they also result in reduced charge storage capacity. This reduction in capacitance not only affects the overall performance of memory storage but also increases the susceptibility of tiny charges to noise. As charges in smaller cells are more vulnerable to external interference, it becomes increasingly challenging to maintain reliable and stable memory storage.

The increasing demands of modern computing have also led to a significant rise in the number of memory accesses, resulting in higher stress on memory systems. As a result, the susceptibility of DRAM cells to noise and interference becomes a critical concern, with even minor fluctuations in charge levels capable of causing memory errors. The resulting instability in-memory storage can lead to a range of issues, from data corruption to system crashes, making it essential to develop strategies to mitigate these effects.

In recent years, the pressure on DRAM technology has intensified, with the need for innovation and evolution becoming more pressing than ever. The limitations imposed by traditional DRAM technology have prompted researchers and developers to explore new materials and architectures that can address existing challenges and unlock new possibilities. The emergence of new technologies such as ReRAM, MRAM, and 3D XPoint has already shown promise in offering improved performance and energy efficiency, paving the way for a new generation of memory solutions.

New Capacitorless DRAM Cell Demonstrated

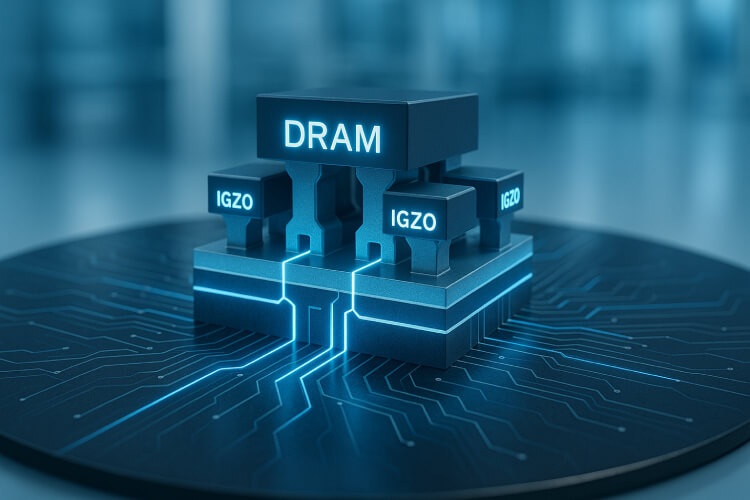

Imec has recently announced the development of a new DRAM technology that utilises IGZO-based transistors. The new DRAM cell design is a two-transistor, no-capacitor (2t0c) design that utilises two thin-film transistors, each with an IGZO channel, to store data. The IGZO material is chosen for its wide bandgap and low off-current properties, which allow for a longer retention time and lower power consumption.

Unlike conventional DRAM designs, the 2T0C IGZO-based cells benefit from the low off-current characteristics of oxide semiconductors. This feature significantly enhances data retention and reduces refresh frequency, addressing a long-standing challenge in DRAM scalability and power efficiency.

By eliminating the capacitor, the parasitic capacitance inherent in the read transistor assumes the role of charge storage. This configuration not only simplifies the design but also supports more compact layouts suitable for future high-density memory arrays.

Applications in Next-Generation Memory and Embedded Systems

The new DRAM cell design has been demonstrated to have a retention time of over 400 seconds, which is about 1,000 to 10,000 times longer than traditional DRAM cells. The use of IGZO transistors also allows for the DRAM cell to be fabricated at lower temperatures, making it compatible with back-end-of-line processing. This opens up new possibilities for DRAM architectures, including the use of stacked configurations and embedded DRAM.

With increased interest in edge AI and embedded systems, capacitorless IGZO DRAM presents a promising candidate for embedded DRAM (eDRAM) applications, offering low power consumption, high endurance, and compatibility with logic technologies. These attributes make it well-suited for next-generation computing architectures focused on performance and energy efficiency.

The ability to fabricate IGZO transistors at low temperatures enables integration within the back-end-of-line (BEOL) of logic wafers. This opens new opportunities for monolithic 3D DRAM structures, where peripheral circuitry and memory arrays are vertically integrated to minimise chip area and improve signal efficiency.

Engineering Enhancements and Fabrication Techniques

Imec has already presented a conceptual 2T0C DRAM bitcell based on IGZO transistors at the 2020 IEDM. To enhance this design, researchers have refined the transistor material stack and integration method, achieving gate lengths of 14nm with retention times beyond 100 seconds. These refinements also include conformally deposited thin IGZO channels — a key step towards layered 2D and future 3D DRAM configurations.

Further engineering efforts have scaled gate lengths down to 14nm while maintaining retention times exceeding 100 seconds, validating the feasibility of aggressive density improvements. Additionally, atomic layer deposition (ALD) techniques have enabled uniform deposition of ultra-thin IGZO layers, supporting the move toward vertically stacked, high-aspect-ratio memory cell designs.

Recent enhancements, such as the replacement of ion beam etching with reactive ion etching (RIE), have allowed patterning of sub-100nm active modules with minimal damage, leading to significant retention time gains and further footprint reduction.

Future Visions For DRAM Technology

As we look to the horizon of technological advancements, the future of DRAM holds immense promise for transforming the computing landscape. The challenges faced by traditional DRAMS are not only driving innovation but also opening up new possibilities for memory technologies. The increasing demand for higher densities and faster memories will continue to push the boundaries of what is possible, and the emergence of new technologies such as ReRAM, MRAM and 3D Xpoint will play a crucial role in shaping the future of computing.

3D Integration: A Shift Towards Higher Density and Speed

One of the most significant trends that is expected to shape the future of DRAM is the transition to 3D structures. Building on the challenges and innovation explored earlier, moving from 2D layouts to vertical integration could dramatically expand DRAM capacities, much like NAND flash. This shift could unlock significantly larger storage potential, enabling the creation of devices that are not only faster but also more powerful than their predecessors.

The impact of this transition on engineers will be major. As engineers work to develop new manufacturing and design techniques, they will need to collaborate across disciplines in ways that were previously unimaginable. The challenges of vertical integration will require a new level of expertise, from materials science to chip design, and the ability to work together will be essential for success. This shift could also transform chip production processes, introducing new technologies and techniques that will enable the creation of smaller, more efficient devices.

From Bottlenecks to Universal Storage

The potential for universal storage is another exciting development that could shape the future of DRAM. With vastly increased densities, the possibility of storing entire computing environments directly on DRAM becomes a reality. This would eliminate the bottlenecks that currently exist between memory and storage, enabling instant file access and transforming the way we interact with data.

However, as with any technological advancement, there are also potential drawbacks and trade-offs that must be considered. While 3D integration offers enormous capacity gains, it also introduces new heat and reliability concerns that must be addressed. The increased complexity of 3D structures could lead to challenges in device stability and system design, requiring new solutions and techniques to mitigate these issues.

As we look at tomorrow’s computing landscape, it is clear that advanced DRAM technologies will play a critical role in shaping the future. By driving down latency and making instant file access a standard feature, these technologies will enable devices to operate at unprecedented speeds, transforming the way we interact with information and each other. The possibilities that these technologies hold are vast and exciting, and as we move forward into the future, it is clear that DRAM will continue to be a driving force in the evolution of computing.