RISC-V Researchers publish new RISC-V SoC

RISC-V | 06-06-2022 | By Robin Mitchell

As RISC-V continues to increase in popularity, more architecture implementations are being developed, and one research team has demonstrated a 3-stage pipeline RISC-V SoC with various peripherals. What advantages does RISC-V present as a future CPU architecture, what did the researchers design, and could FPGAs play a key role in RISC-V development?

What advantages does RISC-V present as a future CPU architecture?

While RISC-V was initially released to the public more than a decade ago, it has only been the last two years that its development has accelerated. Compared to other instruction architectures, RISC-V is entirely open source meaning that anyone can develop their own RISC-V processor without paying any licenses or royalties. This lack of fees helps to significantly reduce the cost of entry to RISC-V CPU development, and this effectively opens the CPU market to more companies. At the same time, the use of an open architecture also means that any pre-existing RISC-V code should run on the new CPU with no issues. This makes all RISC-V CPUs software compatible regardless of the physical implementation.

Another significant advantage to using RISC-V compared to other architectures is that its open-source nature means that no one country can ban its distribution or manufacture. This is a problem that the east has faced in particular (Russia, China etc.) as western nations restrict access to key technologies such as Intel and ARM processors. Additionally, foundries located in western allied nations (such as Taiwan) can refuse chip designs that violate IP rights (such as an ARM core), even if that country is not a part of a trade restriction. But the use of RISC-V (assuming that the core was designed by the customer) could never be refused on the grounds of IP violations.

Finally, RISC-V is now seeing large amounts of software support and development, which will help complement the advancement of RISC-V. When RISC-V first came out, the lack of software tools and libraries made it hard to develop, but now that multiple compilers (and even some operating systems) support the architecture, it can be used easily in practical applications.

Researchers continue RISC-V development with demonstration SoC

Recently, researchers from the Department of Electrical Engineering, University of Engineering and Technology (UET) in Lahore, have publicly released and demonstrated their latest RISC-V SoC that incorporates a 3-stage pipeline RISC-V processor and various memory-mapped peripherals.

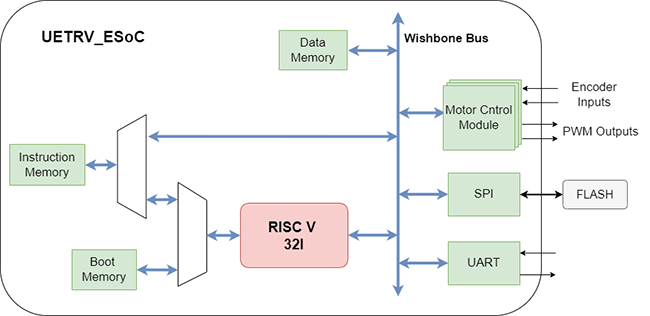

The SoC, called UETRV_ESoC, incorporates a RISC-V 32-bit processor, a Wishbone Bus, and various multiplexers for switching between off-chip FLASH and booting. Peripherals on the SoC include SPI, UART, and three motor control modules that provide PWM outputs and encoder inputs. All peripherals have been memory-mapped, and the internal bootloader is pre-initialised to automatically load external programs without needing the user to code a bootloader.

The designs for the SoC have been released on GitHub (https://github.com/ee-uet/UETRV_ESoC) and include all the files needed to implement the RISC-V on an FPGA. Programming flash can be done using the Texas Instruments TivaC embedded board.

“In an era of a severe shortage of IC designers, design verification experts, and fabs, we must grab the opportunity to produce graduates in this important area of engineering and technology and re-train graduated engineers” - UET Vice-Chancellor Dr Syed Mansoor Sarwar.

Could FPGAs play a key role in RISC-V development?

If there is one technology that has been pivotal in RISC-V development, it’s FPGAs. Their ability to allow for programming hardware circuits without needing to commit a permanent design allows for hardware verification which could never be done in simulation. Once a design has been verified, it can easily be transposed into a silicon design using a silicon compiler, which helps produce a physical device that will likely work the first time.

Additionally, the ability to create a RISC-V in an FPGA allows it to be connected to external circuitry and prototypes for more advanced computing systems. From there, the physical behaviour of the processor can be characterised and tested with real hardware.

There is no doubt that RISC-V development is being helped with FPGAs, which was clearly demonstrated by the researchers who had used an FPGA to test their processor. But if the price of FPGAs fall, it could also start a hardware revolution where circuits are programmable. Users who want to upgrade their processor to a newer standard that fixes security flaws or upgrade their wireless controllers to support new protocols could simply flash the device with new firmware.

If reprogrammable hardware ever becomes popular in consumer products, RISC-V would likely play a central role thanks to its open-source nature. Until then, RISC-V development continues to show signs of strength and may present a real threat to other processor architectures.