Maximising FPGA Performance with Enpirion's PowerSoC Modules

27-10-2015 | By Bob Blake

FPGAs and SoC devices are evolving to add mixed signal functionality to the programmable fabric and unleashing system-level performance that was previously unattainable. However, in order to reap the performance rewards from these complex devices, the designer needs to take into account their particularly stringent power requirements. While the voltage and current specifications are critical factors to consider, the fine details come from the limits of accuracy, ripple tolerance, and transient response.

Understanding the Power Requirements in Advanced FPGA and SoC Designs

With such increasing system complexity and performance, the power requirements can be significant. For high-end applications, FPGA power is a major consideration since, just for the core, it can be in the tens of amps. Add to that hard processors, transceivers, built-in IP and other I/O interface standards, and the final power budget might be over 100 amps. It is understandable, therefore, that any techniques available to improve overall power consumption and device efficiency can have a large impact. For example, a 1% improvement in efficiency can reduce power consumption by up to 270 milliwatts.

The Shift to Integrated Power Solutions for Space-Constrained Designs

The other characteristic of powering an FPGA design is its sensitivity to electrical noise. Firstly, FPGAs have tight supply tolerances, so the power source needs to have high accuracy and low ripple to meet this. Secondly, the operational load on the FPGA can change dramatically, resulting in very fast transients on the power rails. FPGA applications can be very data algorithmic intensive; however, such a workload is not always deterministic, so the power demands of the device can be varied and sudden. Sudden switching will clearly cause transients, and the power supply needs to be able to respond to these by having a high feedback bandwidth to recover quickly. The optimum supply should be able to do this with the minimum number of additional components, such as bulk capacitors. The FPGA core, transceivers and PLLs are susceptible to such transients, so they need to have very clean power rails in order to prevent jitter from entering the system.

Leveraging Innovations for Efficient Power Consumption in FPGA Devices

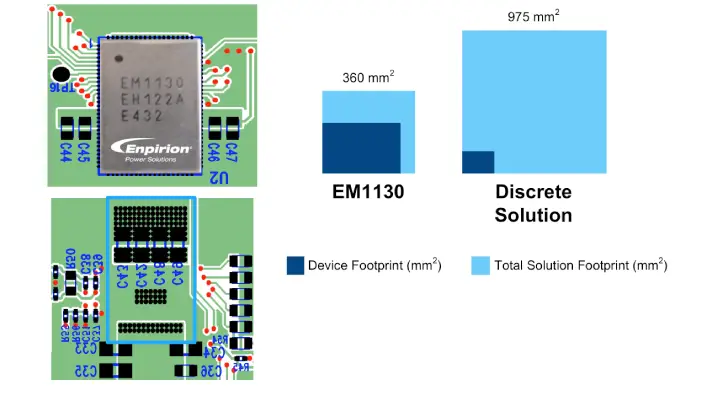

The final consideration for the designer is that, as the FPGA moves to the heart of a system, there is likely to be more I/O standards needing to be supported. Typically, this leads to an increase in the number of power rails. Most designers today will be familiar with accommodating such complex designs in space-constrained enclosures, so in terms of achieving this, the need for a compact integrated power solution ensures that the required board space can be kept to a minimum. For simpler, lower-power designs, the use of a discrete power supply has been a viable approach. Although potentially lower cost, design tasks such as characterising the inductor can take a lot of design time and typically one month longer compared to using and designing in a power supply module if the engineer is starting the design from scratch. However, the added challenges of controlling ripple and achieving the rail tolerances required by the FPGA across all load conditions are extra complications for the designer. Using an integrated module, where the switcher, controller and magnetics are integrated into a single package, is becoming a viable, reliable and more compact option. For example, the Enpirion family of PowerSoC modules operate at a high frequency than traditional DC-to-DC converters. This ensures the magnetic circuitry can be kept as small as possible and integrated directly into the module. By comparison to a discrete solution, the new digitally controlled EM1130 module typically occupies 360 mm2 for a 30 A output supply (see Figure 1).

Figure 1. Using a power module saves valuable board space.

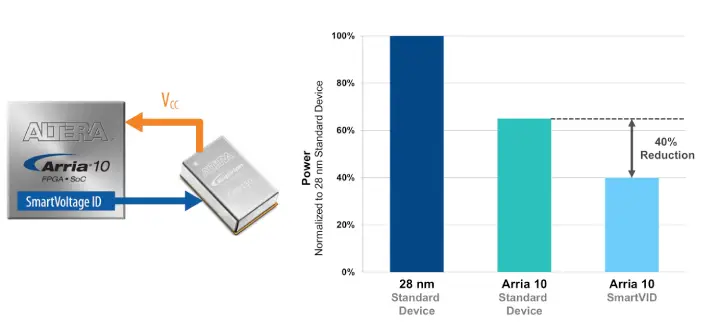

At the power points, today’s FPGA devices work with any technology that can reduce power and can have a significant impact on the overall power budget. One example of an innovative approach is being able to support the voltage ID feature (VID) of a device. This is achieved by additional testing of the FPGA devices during manufacture. By monitoring the core voltage at which each device hits the speed grade, a specific register can be set on the device to state that voltage. This variation in core voltage for a set performance criteria can have a significant effect on the power required. For example, an Altera Arria 10 FPGA can see a power reduction of up to 40% in static power by using the VID feature (see Figure 2).

Figure 2. Using innovations such as VID can significantly lower the power budget.

Naturally, for this to work, the power supply must be able to read this voltage and set Vout accordingly. The latest power devices, such as the Enpirion EM1130, employ the industry-standard PMBus protocol to achieve this. This serial-based interface can interact with the FPGA device and set the core voltage based on the individual requirements of the device. Not only can the PMbus be used to control the output voltage, but it can also be used to measure the voltage, current, and temperature of the device. PMbus protocol commands can be used to control individual power modules if the design combines multiple power supply modules on a single rail. This approach also allows freedom from having to configure the power rail during mass production since, in the case of the EM1130, it can hold up to 8 preset power configurations that can be enabled by setting external resistor values.

Embracing New Technologies in Power Management Modules

The power management module needs to use the latest technology and topology in order to match the evolving needs of high-performance FPGA devices. In the case of the EM1130, this involves using the latest LDMOS technology that can operate at higher frequencies than conventional MOSFETs but without the transistor losses (or efficiency drops) normally associated with running transistors at high frequency. This applies as much to the FPGA core as the transceivers.

In the past, FPGA manufacturers might have recommended a low-dropout regulator (LDO) for the transceivers. However, as the number of transceivers on the FPGA increases, then it has become impractical for them to be powered by an LDO. The use of a switching converter becomes necessary to ensure that the transceivers operate without error at the highest data rates.

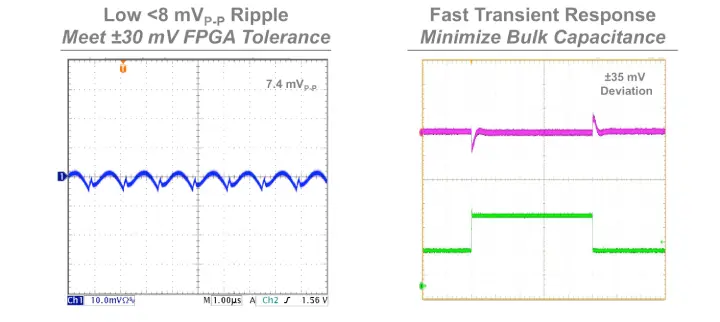

Design engineers selecting a power management module should carefully review the operating frequency for a number of reasons. Firstly, this has a direct influence on the device’s size since the proportions of the required magnetics are related to the frequency. Secondly, operating at a high frequency allows a fast bandwidth feedback path, which means a quick response to transients without the need for physically large bulk capacitors. Keeping the ripple within tolerance, typically within +/- 30mV for most FPGA devices, is essential. For the EM1130, for example, the ripple can be as low as +/- 8 mV, exceeding the minimum requirement by a significant margin and the output voltage within +/- 0.5%.

Figure 3. Tight regulation of ripple and transient response contributes to overall system reliability.

Addressing Thermal Management and Efficiency in Power Design

With tightly packed board designs, thermal performance is another consideration. Clearly, the more efficient a power conversion device is, the more it will influence this greatly. Transfer of heat from the device package to the system PCB aids thermal management. For example, the EM1130 uses a PCB substrate but with a thick copper layer to aid heat transfer. This approach removes the need for a heat sink or any other thermal management techniques.

Paying attention to the power requirements of an FPGA design is an important step of the overall development process but one that will ensure that the application runs reliably over its life cycle.